When light weight AI become your partner. In the office, all people skill become equal. As a result, the inherent kindness in human nature will be hidden!

Preface: High Performance Computing (HPC) systems using AMD chips can utilize AXI crossbars. The AXI crossbar is used to route AXI4-Lite requests to corresponding sub-cores based on the address. This is particularly useful in complex SoC designs where efficient data routing and high throughput are essential.

However, it’s worth noting that AMD’s Versal adaptive SoCs feature a programmable Network-on-Chip (NoC), which replaces traditional AXI interconnects in the programmable logic. This NoC can achieve higher levels of design efficiency and performance compared to traditional AXI interconnects.

Background:

AXI Crossbar

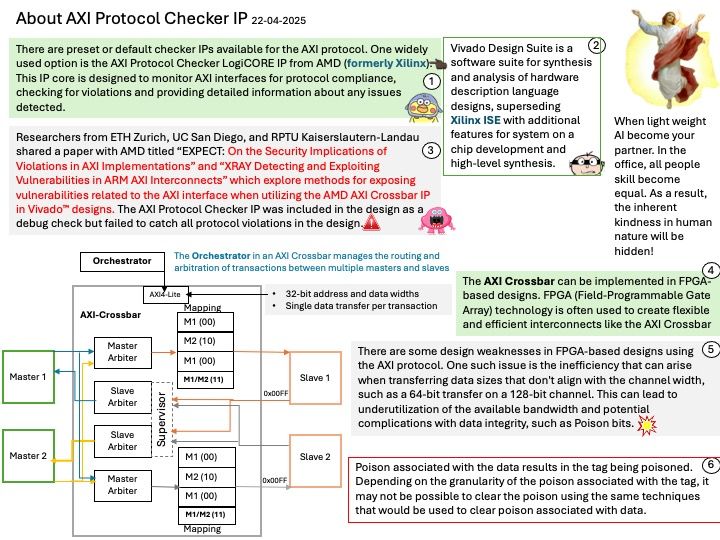

- In an AXI Crossbar, the master interfaces are the sources of transactions, and the slave interfaces are the destinations.

- The crossbar routes transactions from multiple masters to multiple slaves based on address decoding and arbitration logic.

- It ensures efficient communication and data transfer within a System-on-Chip (SoC) design.

AXI4-Lite and the Orchestrator serve distinct roles within an AXI Crossbar:

AXI4-Lite: AXI4-Lite is a simplified subset of the AXI4 protocol designed for low-complexity, low-throughput applications. It supports:

- 32-bit address and data widths.

- Single data transfer per transaction, making it ideal for control register access and configuration tasks.

The Orchestrator in an AXI Crossbar manages the routing and arbitration of transactions between multiple masters and slaves.

Vulnerability details: Researchers from ETH Zurich, UC San Diego, and RPTU Kaiserslautern-Landau shared a paper with AMD titled “EXPECT: On the Security Implications of Violations in AXI Implementations” and “XRAY Detecting and Exploiting Vulnerabilities in ARM AXI Interconnects” which explore methods for exposing vulnerabilities related to the AXI interface when utilizing the AMD AXI Crossbar IP in Vivado™ designs. The AXI Protocol Checker IP was included in the design as a debug check but failed to catch all protocol violations in the design.

Official announcement: Please see the link for details – https://www.amd.com/en/resources/product-security/bulletin/amd-sb-8005.html