Preface: Sandia’s Astra is the world’s fastest Arm-based supercomputer according to the technical article, the supercomputer industry’s standard. With a speed of 1.529 petaflops, Astra placed 203rd on a ranking of top computers announced at SC18, the International Conference for High Performance Computing, Networking, Storage, and Analysis, in Dallas.

Background: A crossbar network is a switching network that allows multiple processors to connect and communicate simultaneously without contention. It enables one-to-one interconnections between processors and memory units, and is commonly used in the design of high-performance multiprocessors and network routers.

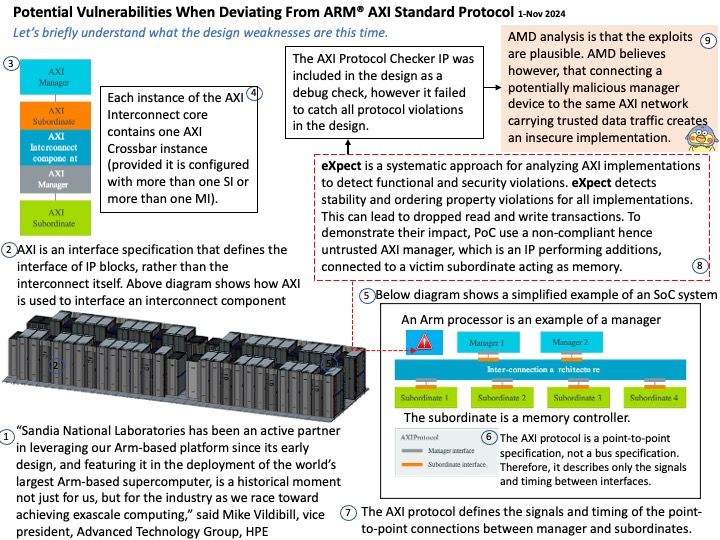

The AXI Interconnect core allows any mixture of AXI master and slave devices to be connected to it, which can vary from one another in terms of data width, clock domain and AXI sub-protocol (AXI4, AXI3, or AXI4-Lite). When the interface characteristics of any connected master or slave device differ from those of the crossbar switch inside the interconnect, the appropriate infrastructure cores are automatically inferred and connected within the interconnect to perform the necessary conversions.

Vulnerability details: Researchers from ETH Zurich, UC San Diego and RPTU Kaiserslautern-Landau shared a paper with AMD titled “EXPECT: On the Security Implications of Violations in AXI Implementations” which explores methods for exposing vulnerabilities related to the AXI interface when utilizing the AMD AXI Crossbar IP in Vivado™ designs.

Official announcement: Please refer to the link for details –https://www.amd.com/en/resources/product-security/bulletin/amd-sb-8005.html